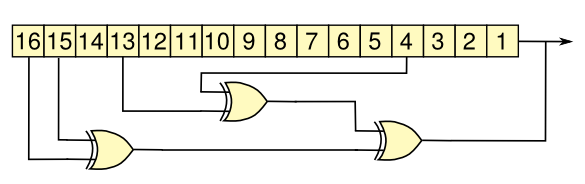

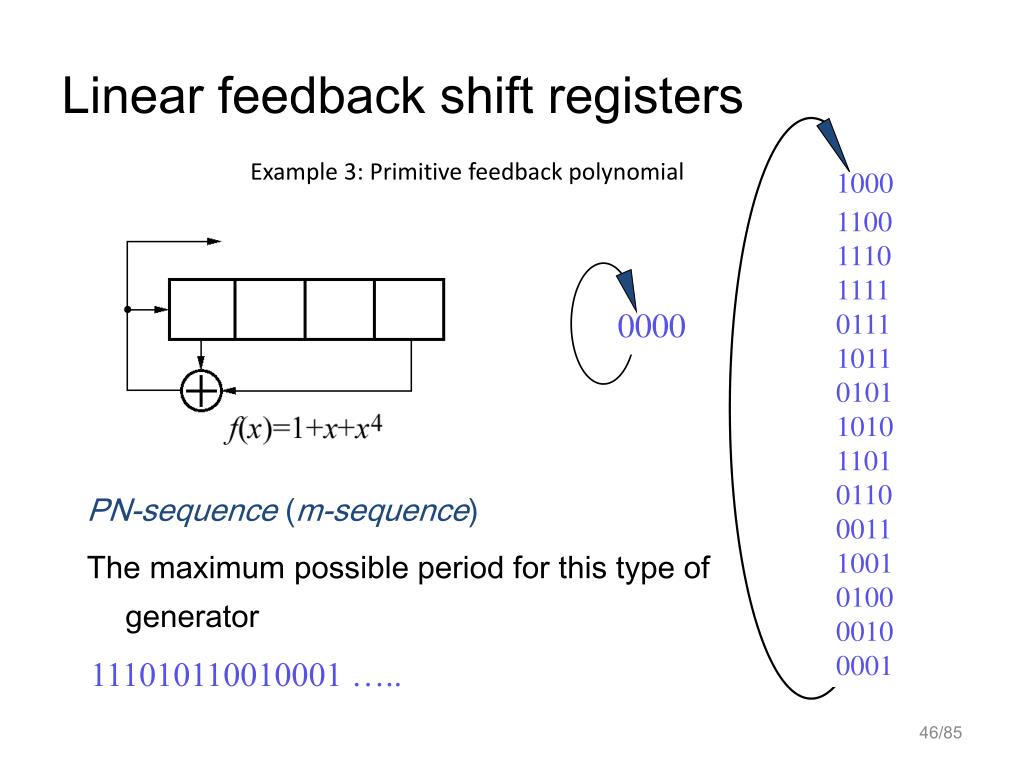

The math involved in analyzing the properties of a LFSR uses Galois fields:Ī simple simulation of a LFSR with two taps: lfsrsim.zipĪ complete list of all dual tap LSFRs up to 42 bit in length and their periods: lfsrperiods. If you need a counter and it does not have to count in a linear way then a LFSR is faster and requires less hardware resources. Tuesday, Design 4-bit Linear Feedback Shift Register (LFSR) using VHDL Coding and Verify with Test Bench Linear Feedback Shift Register is a sequential shift register with combinational feedback logic around it that causes it to pseudo randomly cycle through a sequence of binary values. Only some combinations of taps and lengths will generate a sequence with a period of 2 n-1 cycles.

There are many possible configurations, the one presented here is very simple and has the property that it will start from an input of all 0's and is very easy to implement in software and hardware.Ī LFSR of this type will never contain only 1's and would stall if loaded with that value. A LFSR (linear feedback shift register) is a shift register where the input is a linear function of two or more bits (taps). Geffe generator, composed of three LFSRs of distinct lengths combined by the function f(x1, x2, x3) x1x2 + x2x3 + x3. What is an LFSR A linear-feedback shift register (LFSR) is a shift register whose input bit is a linear function of its previous state.

0 kommentar(er)

0 kommentar(er)